ディジタル回路設計とコンピュータアーキテクチャ 第2版

Sarah L. Harris 著

David Money Harris 著

天野 英晴 翻訳

中條 拓伯 翻訳

鈴木 貢 翻訳

永松 礼夫 翻訳

- 形式:

- 書籍

- 発売日:

- 2017年09月11日

- ISBN:

- 9784798147529

- 定価:

- 5,940円(本体5,400円+税10%)

- 仕様:

- B5・672ページ

- カテゴリ:

- プログラミング・開発

- キーワード:

- #プログラミング,#開発環境,#開発手法,#Web・アプリ開発

コンピュータアーキテクチャの定番教科書、待望の新版!

コンピュータ科学を学ぶ際、心臓部であるマイクロプロセッサの

構造(アーキテクチャ)を理解することは避けては通れない道ですが、

マイクロプロセッサを自ら作成することにより、その理解をより一層

進めることができます。

そんな、マイクロプロセッサを作りながら学ぶ『ディジタル回路設計と

コンピュータアーキテクチャ』が、System Verilogに対応して

バージョンアップしました。

本書は初版同様、特にコンピュータ科学を学ぶ学生のために、

・数の体系、半導体のしくみや論理ゲートといった基本的内容

・ブール代数を実現したり、ラッチ/フリップフロップといった回路設計

・System Verilog/VHDLといったHDL(ハードウエア記述言語)を使った実装

・さまざまな応用的演算回路

・パイプライン処理やメモリ、I/Oシステム

など、マイクロアーキテクチャを作り、理解するための内容を網羅しています。

古典的でありながら今も無数の製品に使われ続けるMIPSアーキテクチャを

中心に、最新の先進的アーキテクチャにいたる解説と、より理解を深めるための

演習や口頭試問、そして豊富なHDL記述例によって、コンピュータアーキテクチャの

基礎をじっくり学べる一冊です。

〈目次〉

第1章 ゼロからイチへ

第2章 組み合わせ回路設計

第3章 順序回路設計

第4章 ハードウェア記述言語

第5章 ディジタルビルディングブロック

第6章 アーキテクチャ

第7章 マイクロアーキテクチャ

第8章 メモリシステムとI/Oシステム

付録A ディジタルシステムの実装法

付録B MIPS命令

付録C C言語プログラミング

第2章 組み合わせ回路設計

第3章 順序回路設計

第4章 ハードウェア記述言語

第5章 ディジタルビルディングブロック

第6章 アーキテクチャ

第7章 マイクロアーキテクチャ

第8章 メモリシステムとI/Oシステム

付録A ディジタルシステムの実装法

付録B MIPS命令

付録C C言語プログラミング

書籍の購入や、商用利用・教育利用を検討されている法人のお客様はこちら

図書館での貸し出しに関するお問い合わせはよくあるお問い合わせをご確認ください。

利用許諾に関するお問い合わせ

本書の書影(表紙画像)をご利用になりたい場合は書影許諾申請フォームから申請をお願いいたします。

書影(表紙画像)以外のご利用については、こちらからお問い合わせください。

お問い合わせ

内容についてのお問い合わせは、正誤表、追加情報をご確認後に、お送りいただくようお願いいたします。

正誤表、追加情報に掲載されていない書籍内容へのお問い合わせや

その他書籍に関するお問い合わせは、書籍のお問い合わせフォームからお送りください。

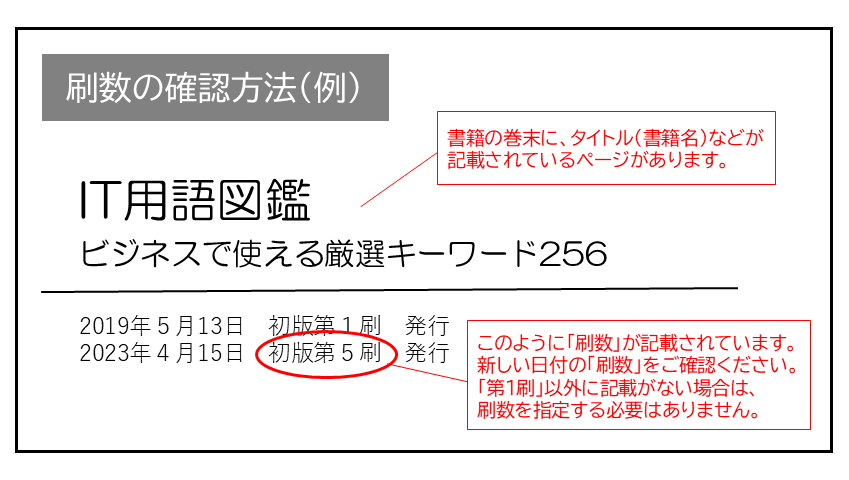

現在表示されている正誤表の対象書籍

書籍の種類:紙書籍

書籍の刷数:全刷

書籍によっては表記が異なる場合がございます

本書に誤りまたは不十分な記述がありました。下記のとおり訂正し、お詫び申し上げます。

対象の書籍は正誤表がありません。

| ページ数 | 内容 | 書籍修正刷 | 電子書籍訂正 | 発生刷 | 登録日 | ||||||

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0-viii オンライン補助教材のURL |

|

2刷 | 済 | 1刷 | 2019.05.07 | ||||||

| 007 「1.4.2 2進数」の本文下から2行目 |

|

3刷 | 済 | 1刷 | 2021.01.08 | ||||||

| 126 表3.13 最下行 |

|

2刷 | 済 | 1刷 | 2019.07.12 | ||||||

| 133 「3.4.6 有限状態マシンの復習」 箇条書き 下から2つ目の項目 |

|

5刷 | 済 | 1刷 | 2022.04.15 | ||||||

| 235 例題5.1 解法 下から2行目 |

|

5刷 | 済 | 1刷 | 2022.04.15 | ||||||

| 285 【リフローのみの正誤】コード例6.3ヌケ |

|

1刷 | 済 | 1刷 | 2026.03.17 | ||||||

| 289 コード例6.6 |

|

未 | 済 | 1刷 | 2026.03.17 | ||||||

| 290 コード例6.8 |

|

未 | 済 | 1刷 | 2026.03.17 | ||||||

| 309 例題6.7 本文1行目 |

|

未 | 済 | 1刷 | 2026.03.17 | ||||||

| 314 コード例6.26 4行目 |

|

5刷 | 済 | 1刷 | 2022.04.15 | ||||||

| 314 コード例6.26の下の文章 2行目 |

|

5刷 | 済 | 1刷 | 2022.04.15 | ||||||

| 315 3行目 |

|

未 | 済 | 1刷 | 2026.03.17 | ||||||

| 479 「8.4.6 マルチレベルページ表」の続き 下から6.5行目 |

|

5刷 | 済 | 1刷 | 2022.04.15 | ||||||

| 498 【リフローのみの正誤】コードの3ブロック目、4行目 |

|

1刷 | 済 | 1刷 | 2026.03.17 | ||||||

| 576 2~3行目 |

|

2刷 | 済 | 1刷 | 2021.03.17 |

れんちゅ さん

2019-11-12

訳がゴミ。研究室の学生が章立てをしてくれたって書いてあったけど、実際のところ殆どすべて学生がやったんじゃないの?と邪推したくなる程度にはひどい。主語と末尾があっていない。文が捻れている。文字を訳しているだけで日本語として美しくない。語学の出来ない人が訳書を出版しないでほしい。

tabularavum さん

2018-01-08

パタヘネ4章を回路の実装の詳細の面で補完するための本。ビルディングブロックの実装の詳細も基礎から教えてくれ、さらに回路図やVHDLのコードレベルできちんと載っているのが面白い。